The problem with EDRAM is that it is a concrete idea, but at the same time broad. For this reason, its use throughout history has been very different, promoting various chips in an entirely new way.

So, it's worth explaining what exactly it is and how it can help 3D installation from Intel and AMD.

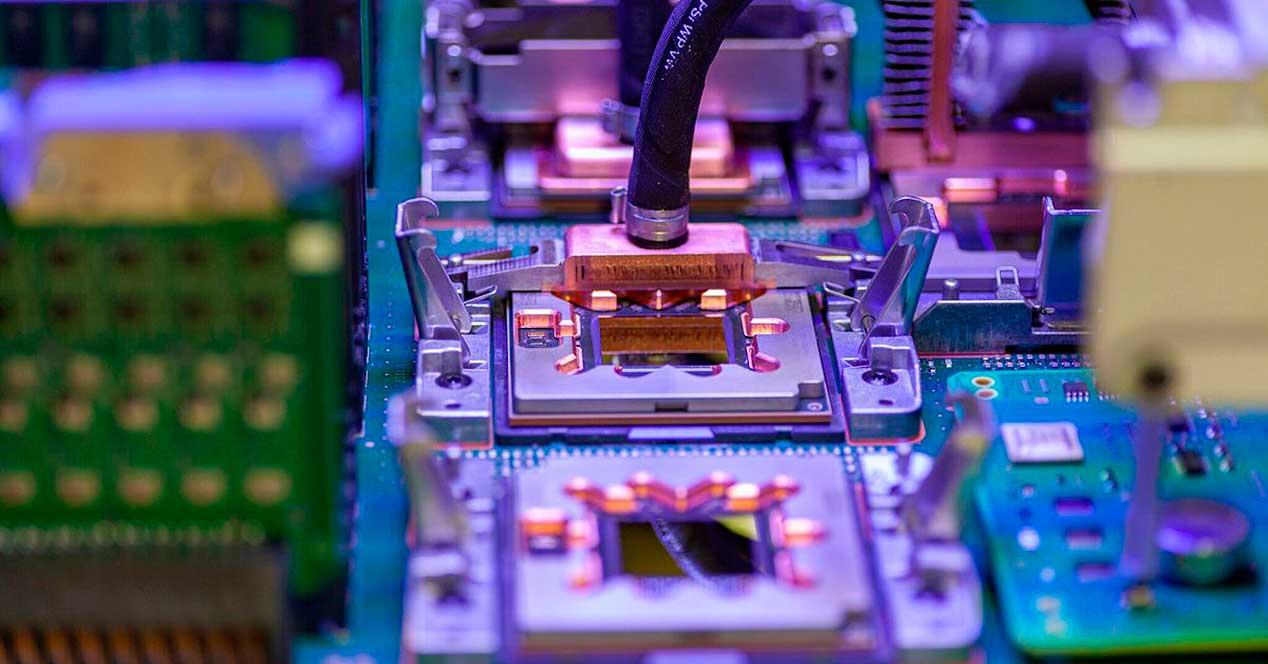

EDRAM: a kind of extra and flexible memory

EDRAM dictionary of Dynamic advanced access memory, the translation will be enhanced by a powerful random access memory. It has the unique advantage of being very attractive depending on which of the chips, since you can not only build memory of that type, but also integrate with a broader RAM concept.

This means that we can understand EDRAM from memory ISRAM even certain types of storage. However, they all come together in the same pattern: memory can be added to the PCB and external to the CPU and the iGPU where both can access.

Therefore, depending on the type of chip used, the manufacturer can choose different types of memory and access. Logically, it has trouble access times, because it's not part of the same die, but when buffer types are required or increasing the curtain size is a very useful way to lose small when the size and registers are wide.

The middle step is to system RAM

EDRAM by definition is a type of memory that acts as an intermediary to the program's primary memory. With the reduction of nanometers this type of memory has been used, but i 3D installation And the amount of chips they can hold as HBM is likely to return it just like that, a buffer when both parties reach.

For this to happen, Intel and AMD will both have to be in serious trouble with their ICs and their IMC, because centralized controller is required to control access.

This is something we have seen in similar consoles PS2, Wii U, Xbox One or Intel and HaswellTherefore, its use may be of great importance in different contexts, thereby increasing the efficiency or limitations of the limits for various construction reasons.

To conclude, EDRAM is a memory that is costly to produce due to the bandwidth to which it is supposed to be supported by the minimum latency, and where the refresh rate is required as standard cells for system RAM.

Therefore, its architecture and its ICs are important to simplify processes without it, making it independent and accessible to different parts of the system.