As we say, TSMC has revealed just about everything about its new lithographic process, which, as happened with its 7nm, will set the standard again next year for AMD and possibly NVIDIA.

So much so, that the company is moving faster than the current and historic line of the Moore Act, which is itself impressive. So let's dive into more details about what's coming and how AMD can be at the forefront of the industry if Intel and Samsung don't respond in a very short span of time.

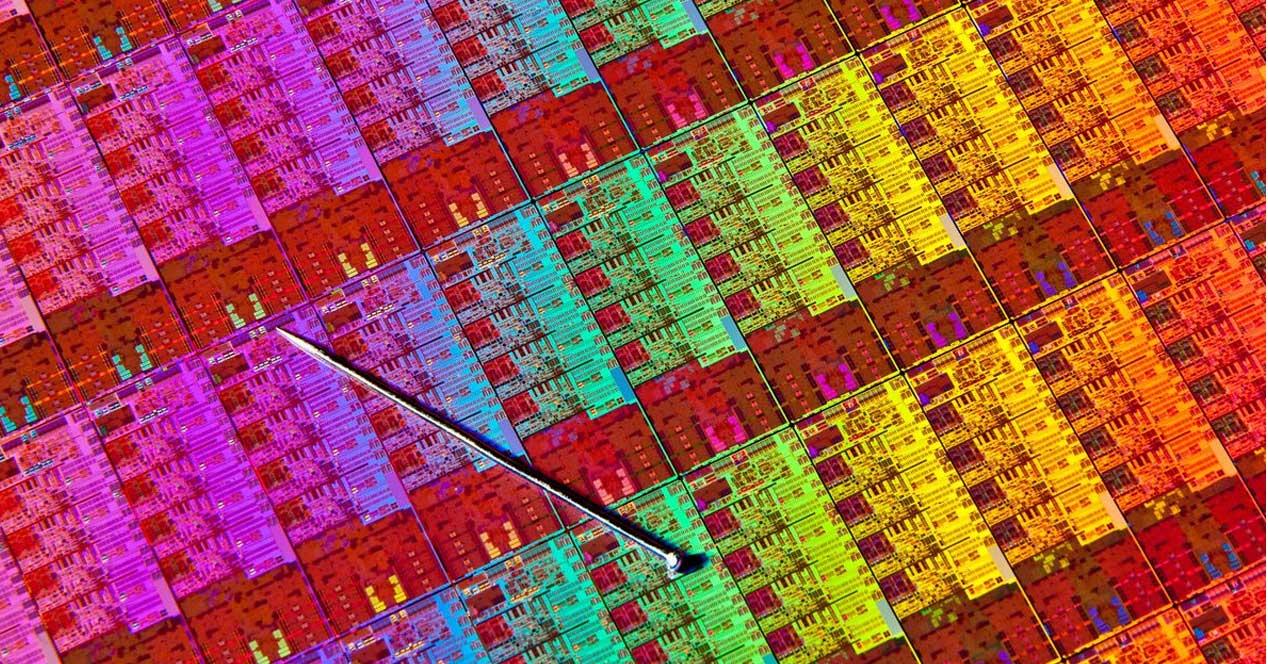

TSMC 5nm: nearly double the speed of the current 7nm

It's only been 5 years, I repeat, for 5 years, since the company introduced its 16nm FinnET into the market with a network of 28.8 million transistors in mm2 until this year that we will see the first finalists to leave their factories by -5 nm.

Although the company has not yet provided details on the scope of this new lithographic process, estimates made by various sources place it at 171.3 million transmi tors per mm2. That's almost double compared to 91.20 MTr / mm2 for the current 7nm process, that is, TSMC will reach almost unity in humans in just two years.

True, he said the lithographic process would be the first to be fully performed using EUV and that means lower and higher grades for each shimmer than has been seen so far. Fin Pitch will be about 25 or 26 nm and only when Metal Pitch is 30 nm there is an equilibrium expression for a particular cell type depending on the type of process selected: SoC or HPC.

And it turns out that this 5 nm node appears to be refined in mid-2020 when the company confirms the high-quality, robust and high-quality lithographic process.

This is a descriptive step for building high-performance processors and it's amazing not to appear first as a replacement for smartphones or low-power processors, as is often the case in the industry.

It holds 12 inches per piece and will only be made in Taiwan

It will be TSMC's Fav18 at the South Taiwan Science Park where it will continue the work of AMD processors and other companies next year. As we well know, the SoC is made up of three main components: logic, SRAM and analog / IO, where each component has different percentages that must complete the SoC.

As reported by TSMC, these estimates for the portable SOC at 5nm will be 60% / 30% / 10%, which compared to the current 7nm would mean a 35% to 40% decrease in chip size.

The development doesn't end here as TSMC means that devices that integrate their node will provide speeds of up to 15% or rather, 30% power at the same speed.

As if that is not enough, it is possible that using eLVT (not iLVT) at high speed can be achieved, up to 25%, or 10% at bulk costs.

This feasibility is possible because 10 EUV layers to be used instead of 40 may be required for the same lithographic process but for the DUV. Because of this, the N5 will be the first lithographic process to use fewer layers than the previous one.

ISRAM

We will have two types of SRAM variants, which will depend on the type of cell desired by the chip compiler and therefore, broadly speaking, TSMC will provide maximum performance and maximum size. Logic tells us that this will be used at different stages of processors or SoCs due to different production metrics.

Following the same graph, it seems that about 4.5 GHz can be achieved with 1V, something that is simply another level compared to what we currently have on the market.

In summary, TSMC will arrive in 2021 with a lithographic process one-and-a-half minutes before the break, when Intel can use its 7nm EUV with great luck and effort and Samsung is currently, an unknown amount, because it is focused on its efforts. in DRAM as in other high-performance chip wafers.

If none of its competitors arrive on time, AMD can dominate the market with a Zen 4-core metal fist and later the RDNA 3 with the Navi 3X from earlier this year. The speed set by the TSMC does not seem to be unbreakable and you are already thinking about its 3 nm, the world is quite impressive.