A number of factors should be borne in mind, which are described in more directly:

- There will be a node high performance

- High volume production will come 2020 Q2.

- There will be a higher performance version next year, N5P a reduction in the frequency + 7% or 15% in the use of the same frequency.

- The quantity increased to 1.8XSRAM 0.75 and 0.85 analog vs. 7 NM.

- Usage between 15 and 30% decreased at the same speed compared to 7 nm.

- be used only EUV.

- A 1.5V or 1.2V I / O transistor and LVT device is 25% faster than the current 7 nm.

- new things Low-K.

- Graphene layer to minimize contact with copper.

As we see, growth is phenomenal, but let's get into one of their depth more.

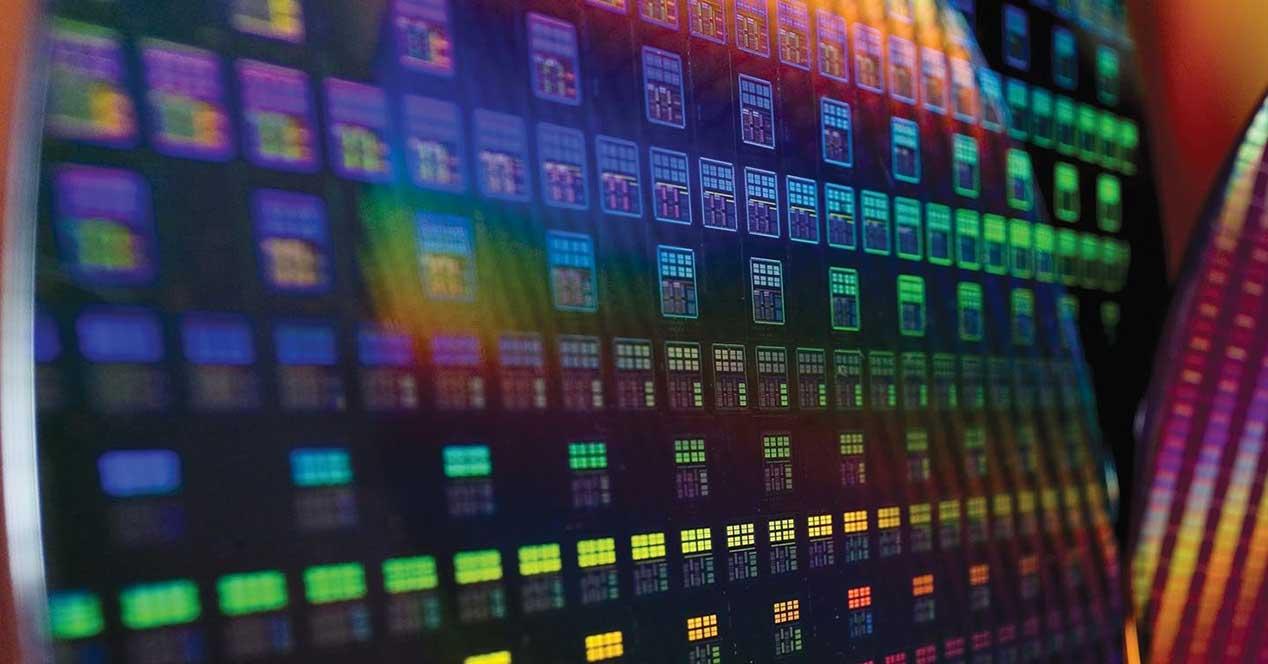

special use EUV, face immersion ran 5 NM

I-5 nm TSMC true ingumlandeli of 7 nm EUV this company and even though they may seem obvious, there is at lea st the conversion of the 3 contrasting or lithographic processes.

This location will be required SAQP or LE3

This involves several improvements, where the microscope is noticeable that the resultant pattern is indeed sharp (up).

This is found in another aspect to be considered, because the number of layers to be used greatly reduced. Therefore, a pure procedure will be done in EUV, if you need no immersion, which you like to withdraw the entire face value, simplify its design.

Current Drive has been upgraded with germanium

The -Drive current or also known as the current fin drive developed by a 18% is a human germanium based, which is mixed with silicon.

This contributes to the height of the transistor deputies, which adds to the difficulty in forming, something the TSMC did not clarify beyond just making a step forward in this phase.

It is even alleged that a recording of the wings of the EUV, which would have created a complete revolution.

Apart from this, SRAM cell size will be the lowest it has been created so far, only 0,021 μm2Below, what Intel Samsung will offer its competitors processes.

Because of this, the PAM4 SerDes can reach speeds of up to 130 GB / s, which may still be available so that they can access Original 112 Gb / s years in the area of 5 nm.

Up to 40% off chip size

Progress in the end here, because the features of this node in the DTCO (Design Technology Co-Optimization) receive scales new smart design, and will be based on what has been done to the mobile SoCs with Logic 60%, 30% and 10% SRAM-I / O analog.

The result is that the physical size of the chip can be reduced 30 and 40%. The pace will be another climax of this area. TSMC ensures an increase in the maximum speed of + 25% compared with 7 nm, when and if they are able to enter the cell 3 standard fins another 10% added an HPC will be available.

In summary, TSMC will also take the lead as the best place in the world, at least ahead of Samsung, because Intel has not mentioned that we can see through its EU 7 nm, a lithographic process that raises many expectations.

In addition, the improvement in the 5 nm TSMC position is therefore against its Korean competitor as the cost of each wafer is somehow lower, so it will not only shrink, but also cheaper its customers.