We are used to RAM changing every x years in the form of a new generation of DDR, GDDR or whatever type of memory is used at any given time, but that could change as the use of certain technologies will be necessary for it to continue to evolve.

How has RAM evolved all this time?

RAM, being a semiconductor, evolves according to the Moore’s Ley and at the same time of the Dennard scale, this means that on the one hand the density of the transistors increases and with it the storage capacity of the memories, while on the other hand the communication speed is improved, what we call the band width.

The idea is very simple, in each new manufacturing node the voltage needed to reach a specific clock speed decreases, so we can create a RAM that consumes the same and is faster or another that is just as fast but consumes much less.

But the problem comes with increasing the speed, since the RAM bandwidth of a system depends on the power consumption of the communication between the memory and the processor to which it is allocated, hence the amount of width of the system. the tape with each new node is limited and this occurs in that the jumps from one type of DDR memory to another become smaller and smaller.

What if we can’t scale system RAM further in the future?

A solution for this use of technologies such as PAM-4 Used in GDDR6X and in future iterations of the PCI Express standard, if you look at it from a certain point of view, PAM-4 is still a type of data compression. In addition, it is said that future DDR6 memory could use PAM-4 communication.

And speaking of data compression, it is very possible that we will see RAMs with logic inside, accelerators designed to make data search more efficient and faster, which can compress and decompress flight data. that is sent. The reason for this is very simple, sending x bytes which is compressed data consumes power in the same way as sending the same number of bytes with uncompressed data.

Are we going to see 3D DRAM as the RAM of the future?

3D DRAM involves stacking multiple memory chips together and using paths through silicon to communicate with the memory controller.

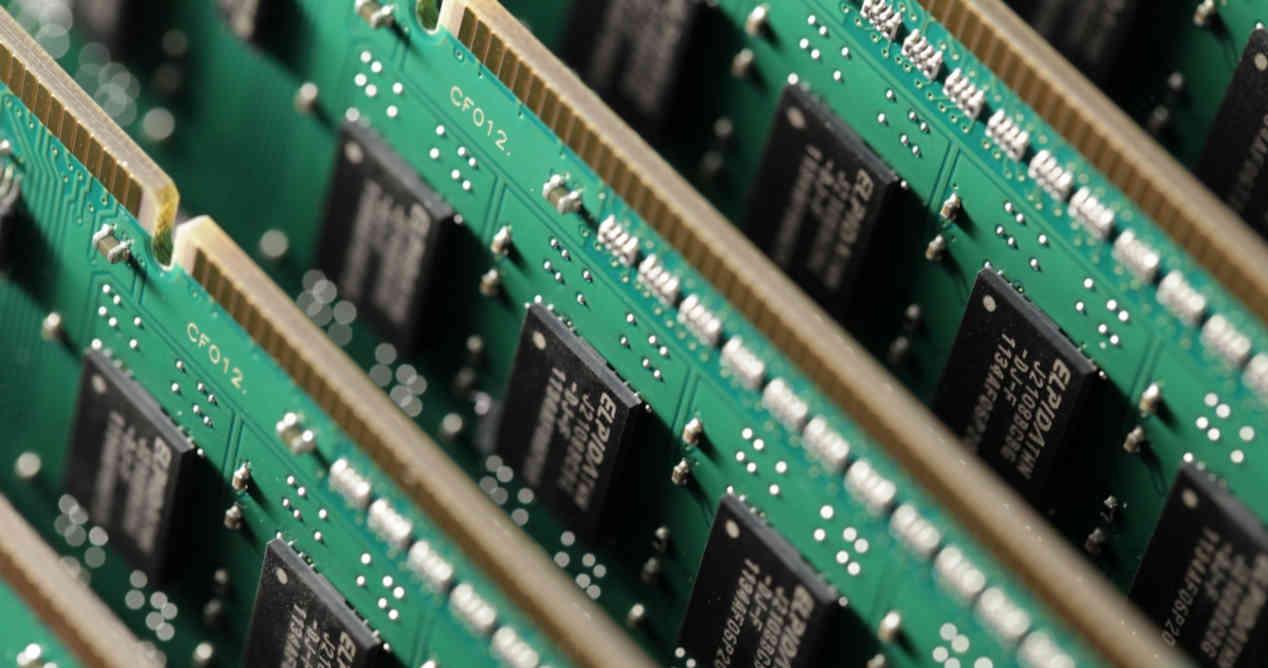

In the case of DDR memories, there are 3DS-DDR standards where up to 4 DDRn chips are stacked (the nth generation of DDR) which are connected to a 64-bit controller. So, with this technology, it would be possible to reduce a total DIMM from 8 chips to just two chips. But this does not bring any advantage in terms of consumption and speed, but it results in extremely expensive memory, which has led not to standardize its use and we continue with conventional memory DIMMs.

3D DRAM only makes sense if it is accompanied by interfaces with a large number of pins, which can transmit a large number of bits per cycle, allowing lower clock speeds and therefore higher voltage to be used. low, but these solutions require a complex interposer and considerably limit the expansion capacities of the RAM.