In fact IMC is one of those parts of the processor that is often overlooked, and that often means looking at the cores, the speed, and the very large cache memory it has. But it's the inside part of the processor that matters most, and below you will find out why.

What is the BMI of the processor

IMC stands for "Integrated Memory Controller," or integrated memory controller. The memory controller can be split or integrated into another chip, so the ones that are included are those that, as you will think, are integrated into the processor's death. Previously the memory controller was available on the board, but for a long time now only IMC has been used, since it allows the processor to quickly and easily control the memory.

IMC is then a digital circuit that controls the data flow that comes and goes between the processor itself and the RAM. Being integrated into the processor allows RAM management to be performed more quickly and faster than when memory controllers were on the motherboard.

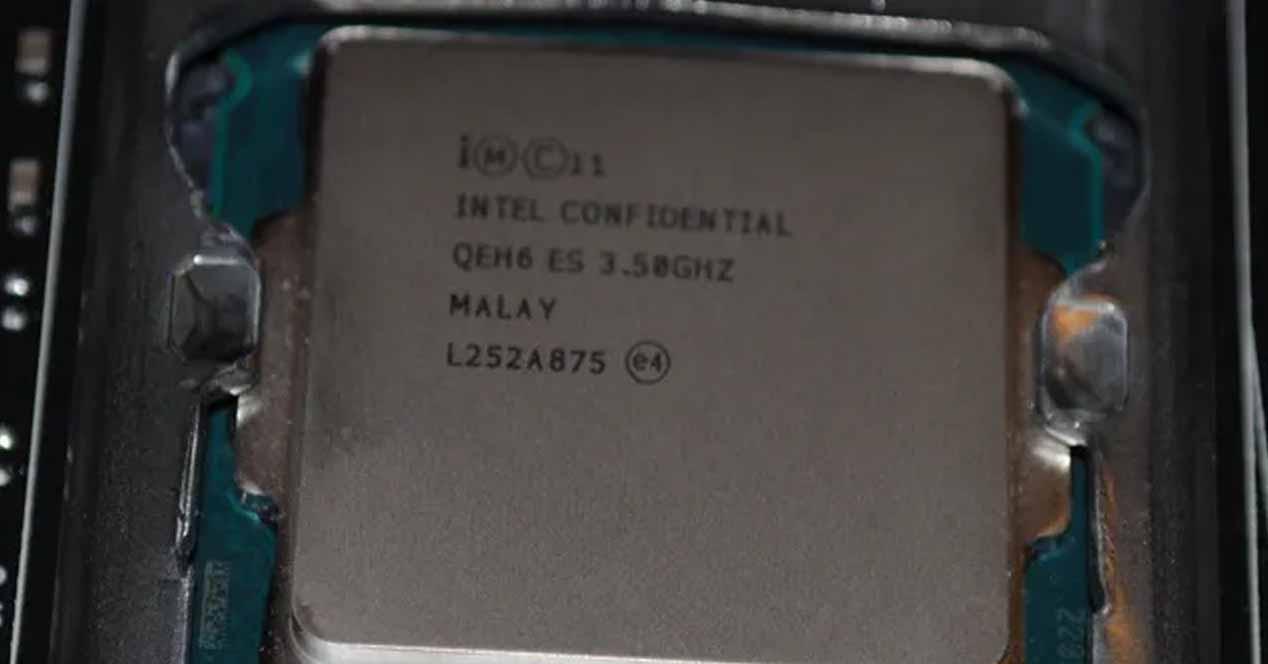

Before the AMD K8s (released in 2003), AMD processors had memory control in their north, but for generations to come AMD is pioneering to install it in the processor itself. Intel first did the same for Nehalem testers in 2008, after which both manufacturers only used IMC. Unfortunately, ARM build controllers also use, in all cases, a memory controller built into the processor.

How does the memory controller work?

Memory controllers have the logic needed to read and write RAM, and "refresh" DRAM. If there were no nutrients like these "drinks" 64 milliseconds according to JEDEC).

RAM read and write is done by selecting the DRAM row and column data addresses as integrated circuit input, where the DRAM demultiplexer uses a modified input to select the appropriate memory location and returns the data, which is retrieved by the merge cursor to reduce the bus width required for operation.

The memory bus memory represents the number of parallel lines available to communicate with the memory cell. The width of the memory-control bus varies from 8 bits in older programs to 512 bits in modern video cards and systems (they usually work as four simultaneous 64-bit memory controllers, though some are designed to work in "group mode" where two memory controls can be used. 64-bit access to 128 memory device).

Some memory controllers also have their own debugging system that can be included with those that include RAM memory modules themselves (which is great because it frees them in some cases, doubles in size to debug others).

Variety of existing BMI

Of course you have noticed that the processors' descriptions almost always include a description of the type and speed of RAM they are compatible with, directly depending on the BMI they enter. So, there are different types of memory control, and some of them you will certainly recognize immediately.

On the other hand there is DDR drivers which can be (usually) two stations y quad channel. The difference is that in this RAM memory is divided into 2 or 4 different channels, each with direct buses to the memory controller. These are widely used on PCs, as well as those we all know.

On the other hand we have FBM controls (Full Full Memory) whose behavior is different than the previous one to include a buffer device in each memory module (called FB-DIMM) which uses a communication and controller data link (rather than the same), reducing the number of robots needed to communicate at the cost of increasing latency.

Finally, we have drivers flash memory, which are used by devices such as pen drives or SSDs. Flash memory is slower than DRAM and often becomes invisible after multiple write cycles, but it still needs to have its own memory controller to communicate with the rest of the system.