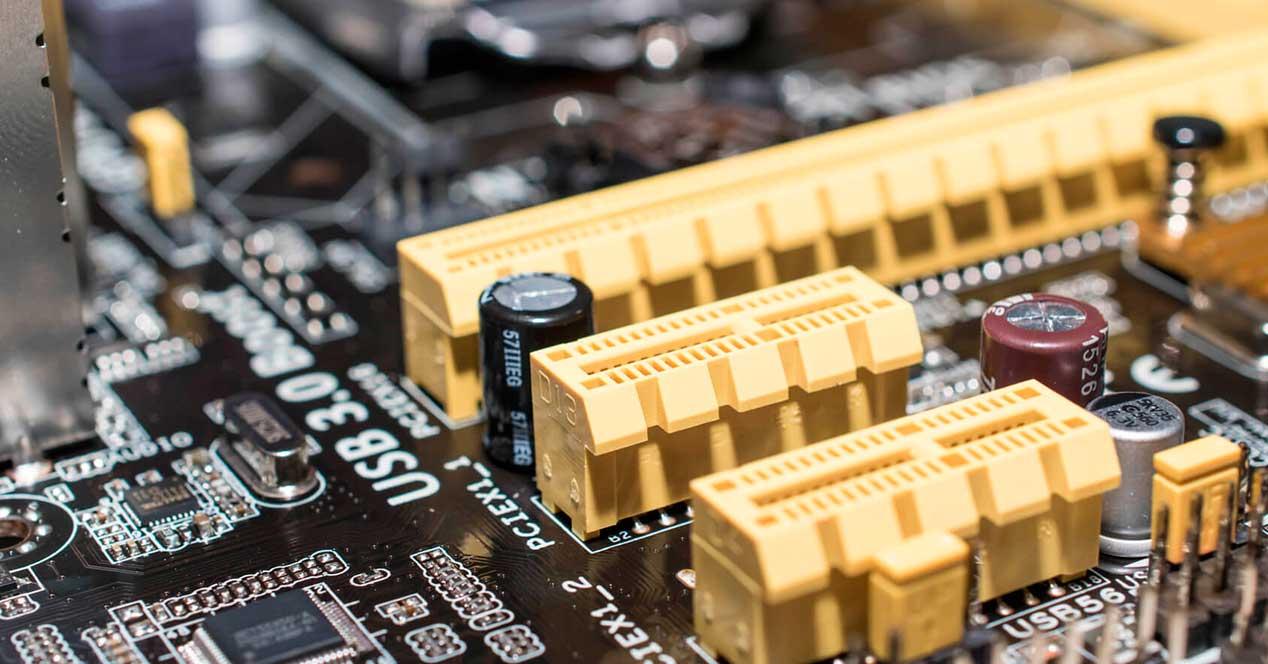

The fact is, for desktop and server, PCI Express becomes the best choice for cutting-edge work AMD has just introduced PCIe 4.0 and next year its fifth version will arrive on servers that will handle new devices, algorithms and interfaces.

Speed and latency are becoming increasingly important in fields such as HPC or IA, so features and versions will not stop happening over the next several years.

PCI Express speed from version 1.0 to 5.0

PCI Express is only for local bus use. Many jobs today come down to some very special situations:

- Picture cards.

- FPGAs.

- High speed SSD.

- SSD extensions.

- Sound cards

Although more is used, they end up being less representative and less representative, so that we know what kind and speed we need, we will know all the forms that have been completed so far on this bus.

As we can see, the big jump came from version 2.0 or 2.1 to 3.0, where coding was increased by 13 and gigatransfer nearly doubled,

Similarly, bandwidths do the same for each channel, leaving a different speed series for each version:

- PCIe 1.0 -> 2 Gbit / s (250 MB / s) per route.

- PCIe 2.0 -> 4 Gbit / s (500 MB / s) per route.

- PCIe 3.0 -> 7.9 Gbit / s (984 MB / s) per route.

- PCIe 4.0 -> 15.8 Gbit / s (1969.2 MB / s) per track.

- PCIe 5.0 -> 31.5 Gbit / s (3938.4 MB / s) by road.

How to calculate the speed of each PCIe line

Although all the details are well represented in this article, it's always good to know how developers calculate the bandwidth for each version and each wine. It's actually quite simple when we have the right data, because it all comes down to choosing a line where we want to know its functionality, choosing its functionality. Gigatransfer multiply it by encoding its corresponding version.

This will give us what is called a different pair or pair, which is displayed in MB / s. Now we have to multiply this number by the number of whole rows we want to calculate, where the data we get will be GB / s and one way.

If we want to know the bidirectionality of a particular bus, we will multiply the value in pairs, because it is synchronous. It continues to know the final specifications of PCIe 6.0, but the first data we have seen makes us think that it will duplicate all the values, save for coding and where new hardware partitions will be needed, as happened with PCIe 3.0 vs PCIe 4.0.

So, compatibility is guaranteed, but we can find that developers do not offer PCIe 6.0 on traditional boards with PCIe 5.0, and by the way, go through the box again.

This is not guaranteed, in fact this year they will be having final meetings to fix details like this, but from a more mature perspective, it looks like this scenario will be for new boards and not BIOS / UEFI improvements for those with PCIe 5.0.